In het tijdschrift Science wordt een nieuwe ‘brein’ chip beschreven, een samenwerking van IBM, Cornell en IniLabs, als basis voor ‘non-von Neumann’ computers.

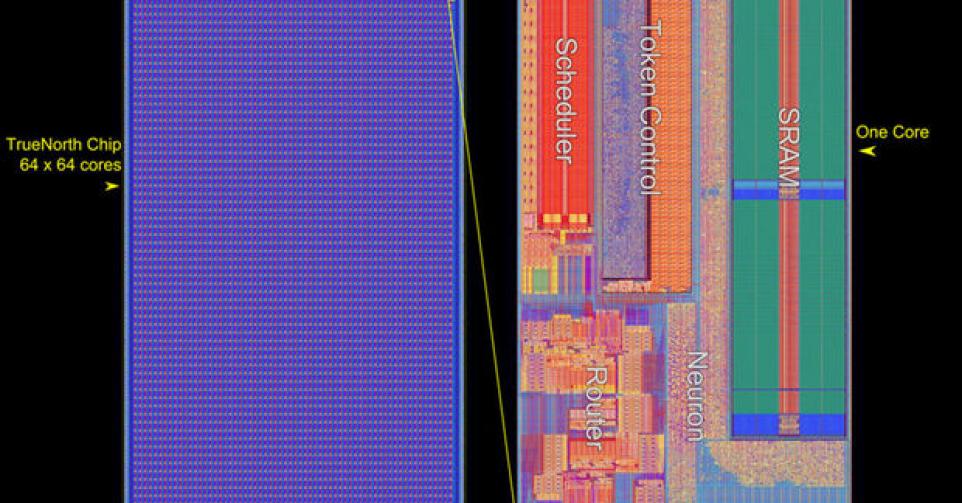

Met 4,5 miljard transistors is deze nieuwste chip – ‘TrueNorth’ – in het SyNapse onderzoeksprogramma (Systems of Neuromorphic Adaptive Plastic Scalable, onder meer gefinancierd door de Amerikaanse militaire onderzoeksafdeling DARPA) meteen ook de grootste chip die IBM ooit heeft gebouwd. De transistors zijn verdeeld over onder meer een netwerk van 1 miljoen ‘neuronen’ (in 4.096 blokken van 250 neuronen) en 256 miljoen ‘synapsen’ (verbindingen tussen neuronen). Dat wijst er meteen op dat deze chip een structuur heeft die gelijkt op deze van (zoogdier-)hersenen. De werking is dan ook massief parallel van aard en verschilt zo fundamenteel van de huidige seriële ‘von Neuman-aanpak’ in processoren. De ‘neuronen’ en ‘synapsen’ combineren de functies van geheugen en verwerking, en communiceren met elkaar door middel van ‘spikes’.

De architectuur van de ‘TrueNorth’ processor werd al eind 2012 gesimuleerd in het kader van het ‘Compass’ project, op de IBM Blue/Q supercomputer in het Livermore Lawrence onderzoekslab.

Neurale netwerken en supercomputers

De processor zou de kracht van 46 miljard synaptische operaties per seconde bieden, gekoppeld aan een uiterst laag stroomverbruik (maximaal ongeveer 70 milliwatts, tegen ongeveer 35 tot 145 milliwatts voor klassieke processoren). Een testtoepassing inzake videoherkenning in het verkeer (400×240 pixel videoinput à 30fps) verbruikte amper 63 milliwatts. Een zelfde toepassing op een klassieke notebook draaide in vergelijking 100 maal trager, en verbruikte 100.000 maal meer stroom.

De onderzoekers zien deze architectuur als bijzonder geschikt voor “toepassingen die gebruik maken van complex neurale netwerken in reële tijd, zoals multi-object detectie en classificatie.” Daarbij kan worden gedacht aan toepassingen inzake beeld-, geluid- en signaalverwerking (zoals uit gedistribueerde netwerken van sensoren, inclusief informatie uit (militaire) onbemande vliegtuigen en andere voertuigen). Door meerdere van dergelijke SyNapse chips te koppelen, beoogt men systemen met supercomputing-kracht te bouwen voor toepassingen die vandaag de kracht (en het stroomverbruik) van grote clusters van krachtige machines vereisen.

De grootste uitdaging wordt allicht de vereiste nieuwe aanpak van software ontwikkeling. Eerder dit jaar kondigde IBM dan ook een aangepast ‘corelet’ programmeermodel aan, en gaat tevens voorzien in een bibliotheek van gebruiksklare stukken code.

Het mag overigens interessant heten hoe recentelijk wel vaker nieuwe ‘non-von Neumann’ architecturen worden voorgesteld, zoals eerder dit jaar nog HP’s ‘The Machine’ .