De chipsector staat voor hoge verwachtingen en uitdagingen. Om aan de eisen van AI te voldoen moeten chips niet alleen flexibeler worden, maar ook (letterlijk) in meerdere dimensies uitbreiden om Moore’s Law aan te houden. Een grote, maar niet onmogelijke uitdaging volgens imec-topman Luc Van den hove.

Het chiponderzoeksinstituut imec houdt deze week zijn grote conferentie in Antwerpen. ITF World is verre van een Belgisch of Vlaams event. Onder de sprekers zitten mensen van onder meer Google Deepmind, Nvidia en Apple, die met enthousiasme komen uitleggen hoe zij vanuit hun domein naar de technologierevoluties kijken. Meermaals valt te horen dat die innovatie in samenwerking met imec tot stand is gekomen.

Maar al die vooruitgang begint bij de chip als bron van alle rekenkracht. De sector kon jarenlang verderbouwen op steeds kleinere transistors waardoor er meer op één chip pasten. Kleiner betekent doorgaans ook energiezuiniger. Maar die transistors nog verder verkleinen wordt fysiek moeilijker. Tegelijk is de vraag naar rekenkracht, compute, groter dan ooit door AI.

‘Met de komst van DeepSeek leek het even alsof de vraag naar rekenkracht zou afnemen. Dat is niet het geval, het zal net zorgen tot een snellere adoptie van AI en dus massaal veel meer rekenkracht vragen,’ stelt Van den hove in zijn keynote op ITF World.

Dat we nog steeds in een beginfase zitten illustreert de topman van imec door er op te wijzen dat er nu verschillende soorten AI zijn die op termijn moeten samenwerken: ‘De volgende generatie van AI zal meer heterogeen zijn. We hebben generative AI, agentic AI, fysieke AI, die kan interageren met de wereld in domeinen als health of automotive. Maar we zullen daarbij meerdere modellen combineren die ook onderling met elkaar interageren op een intuïtieve manier. Dat zal de vraag naar meer rekenkracht alleen maar opdrijven.’

Twee snelheden

Die groeiende vraag dwingt ons om chips en algoritmes te ontwikkelen die minder stroom vragen. Van den hove wijst daarbij op een obstakel:

‘We zijn van CPU’s naar GPU’s gegaan, en naar ASIC-implementaties waarbij de algoritmes hardwired in de chips zitten om zo minder energie te verbruiken. Maar AI-modellen evolueren sneller dan dat je zo’n chip kan ontwikkelen. Tegen de tijd dat je een algoritme in een chip hebt gezet, zijn er weer betere algoritmes. Er is een synchronisatieprobleem en dat moeten we aanpakken. Daarom hebben we nood aan meer flexibele, herconfigureerbare compute architecture in veelzijdige technologieplatformen.’

Ook bij Nvidia zien ze de nood om het als sector anders aan te pakken. Vivek Singh, Vicepresident Advanced Technology bij Nvidia wijst ook op de enorme toename van het aantal transistors per chip en hoe die chips elke generatie complexere berekeningen aankunnen, maar dat dit nog steeds te weinig is om aan de vraag te voldoen.

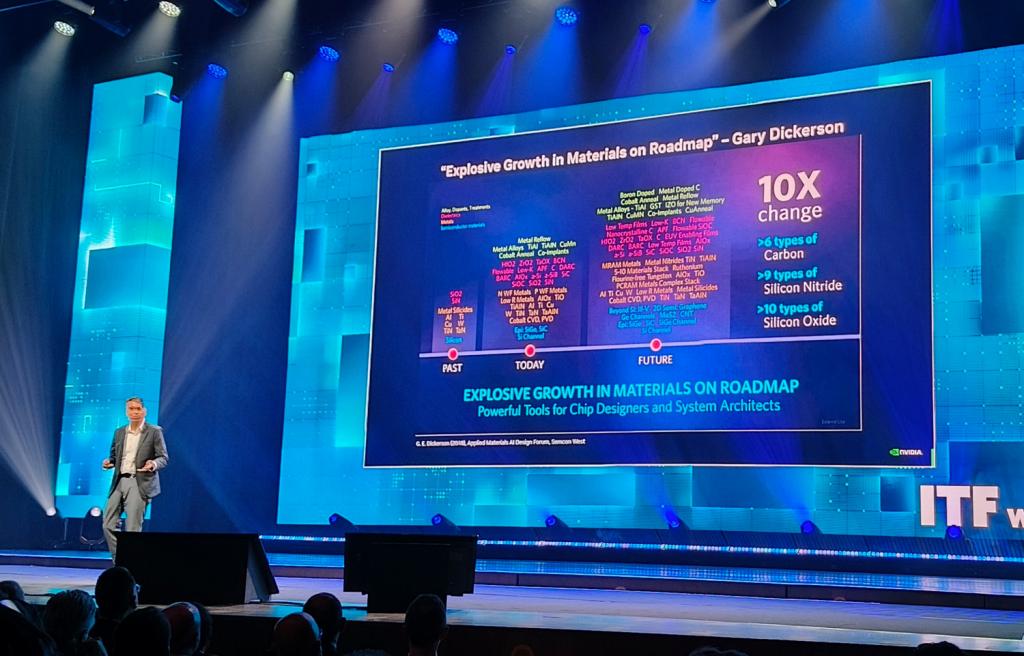

Dat maakt dat AI-datacenters veel meer stroom opeisen dan een klassiek datacenter. Tegelijk worden chips ook fysiek complexer. In het verleden zaten in een chip een handvol grondstoffen verwerkt, vandaag zijn dat er enkele tientallen. Naar de toekomst zullen er honderd of meer verschillende soorten metalen, halfgeleiders en stoffen voor behandelingen nodig zijn.

‘Er moet iets fundamenteels veranderen. We gaan honderden extra datacenters nodig hebben om aan de vraag te voldoen. Een paar van 15 megawatt is nog handelbaar. Maar honderden datacenters die gigawatts vragen, dat gaat de wereld en het klimaat niet aankunnen,’ zegt Singh in zijn uiteenzetting.

2D en 3D schalen

Ook de decennialange beweging naar meer en kleinere transistors op één chip botst op fysieke limieten. Van den hove wijst naar de nauwe samenwerking met de Nederlandse chipmachinemaker ASML om die schaling in 2D mogelijk te maken.

Dat schalen gaat ook in de hoogte, in 3D stacks, ook wel advanced packaging genoemd. ‘We stapelen de transistoren bovenop elkaar en zo krijg je een extra schaling effect bovenop de lithography based scaling (waarbij je meer kleinere transistors op één chip plaatst, nvdr).’

Over die methode wordt al enkele jaren gesproken, maar op ITF World is het duidelijk dat dit de aanpak wordt voor de toekomst en dat de grote spelers in die richting kijken. Scott DeBoer, Chief Technology & Product Officer bij Micron, dat zich vooral op geheugen en opslag toelegt, ziet ‘een sleutelrol’ weggelegd voor advanced packaging om de AI-revolutie te dragen.

Ook in zijn domein wordt er gekeken hoe de ontwikkeling van geheugen(chips) de volgende sprongen kan nemen om de zware vraag van AI te beantwoorden, bij voorkeur in hardware die niet nog meer energie vraagt of warmte genereert. Het is puzzelen met technologie terwijl de individuele stukken zelf nog in ontwikkeling zijn.

Gespecialiseerde lagen

Imec’s Van den hove is enthousiast over hoe het op elkaar stapelen van chiplagen ook nieuwe zaken mogelijk maakt. ‘Elke laag kan zijn eigen specialiteit hebben en zo kan je geoptimaliseerde en vereenvoudigde processen krijgen die op hun beurt verdere opschaling mogelijk maken, dat noemen we CMOS 2.0.’

Van den hove vergelijkt CMOS 2.0 met een ‘FPGA on steroids’, FPGA’s zijn zeer programmeerbare geïntegreerde schakelingen, en dus vlot aanpasbaar aan het einddoel. Maar ook 3D transistors (CFET of complementary field-effect transistor) spelen samen met advanced packaging een rol om een nieuw type chip te krijgen die veel meer aan kan.

‘De manier waarop onze chips worden opgebouwd gaat radicaal veranderen. In een 2D omgeving heeft alles zijn plaats. In 3D kan je denken aan een zee van gestandaardiseerde supercellen, met L1 en L2 memory, network on a chip, functional grains, registers, maar ook een reconfigurable control network.’ Dat laatste is de sleutel tot die aanpasbaarheid.

Voor imec is er niet één richting om chips exponentieel performanter te maken. ‘Het is een en-en-en verhaal. De architectuur, AI-ontwikkelingen, de materialen… maar ook nieuwe concepten zoals superhalfgeleiders of kwantumcomputing kunnen voor vooruitgang zorgen.’

‘De uitdagingen zijn enorm, maar het is een spannend moment om in deze sector te zitten,’ besluit de topman van imec.