Het Leuvense onderzoekscentrum imec heeft samen met chipmachinemaker ASML patronen geprint met behulp van High NA EUV lithografie. Die methode moet de volgende generaties chips mogelijk maken.

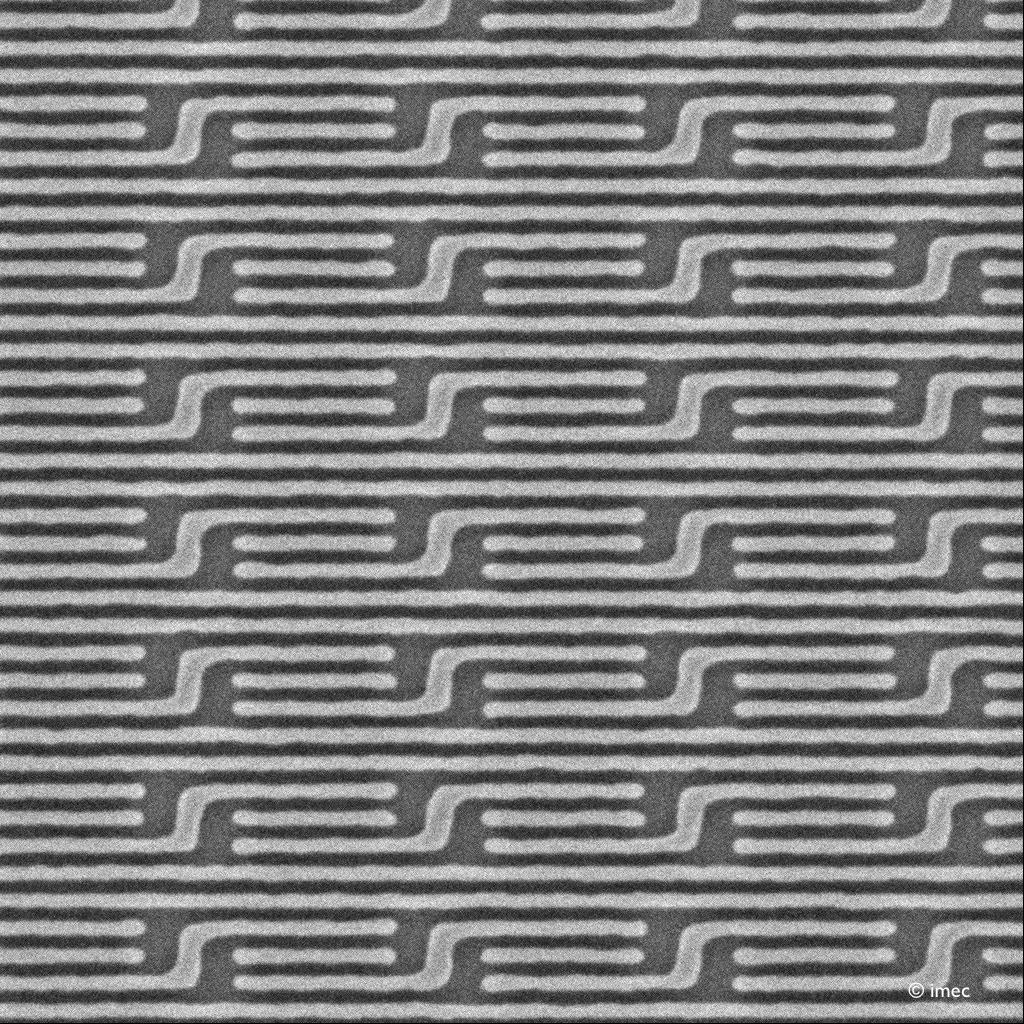

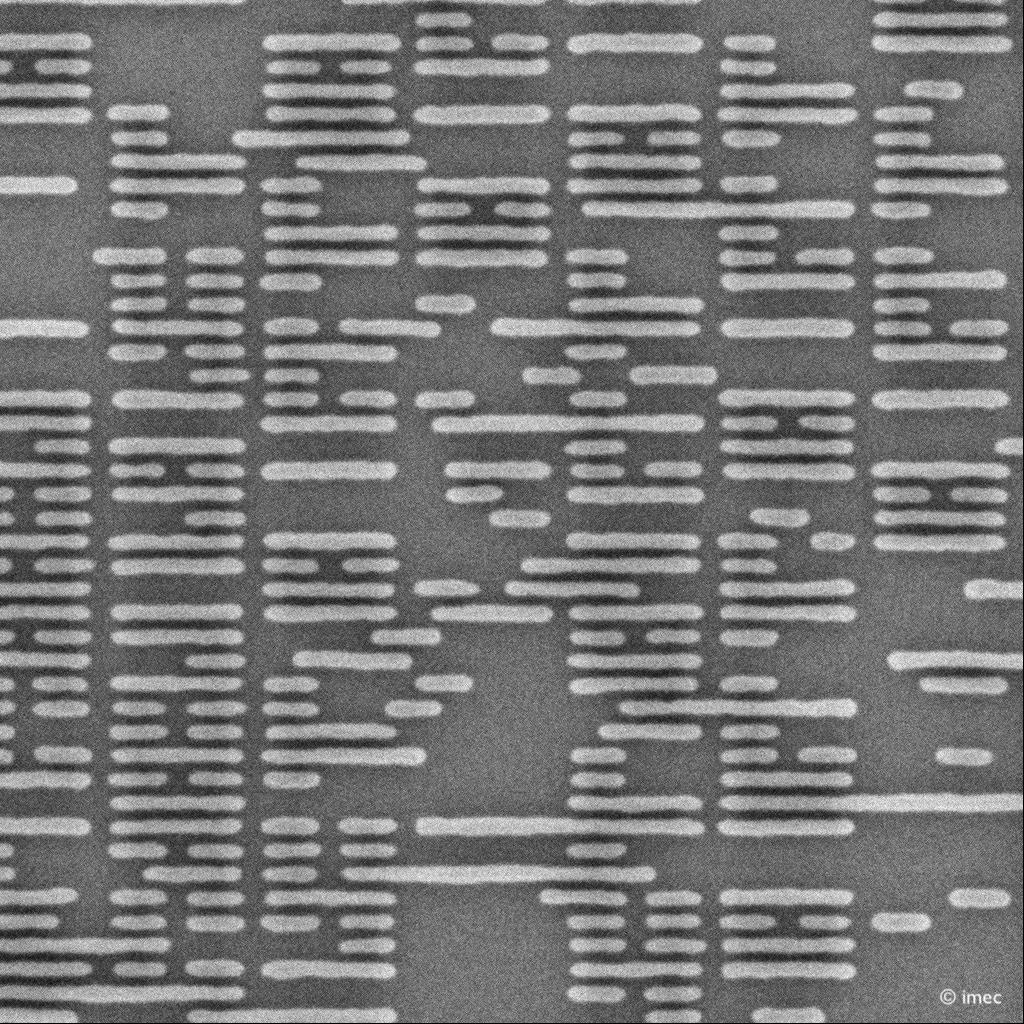

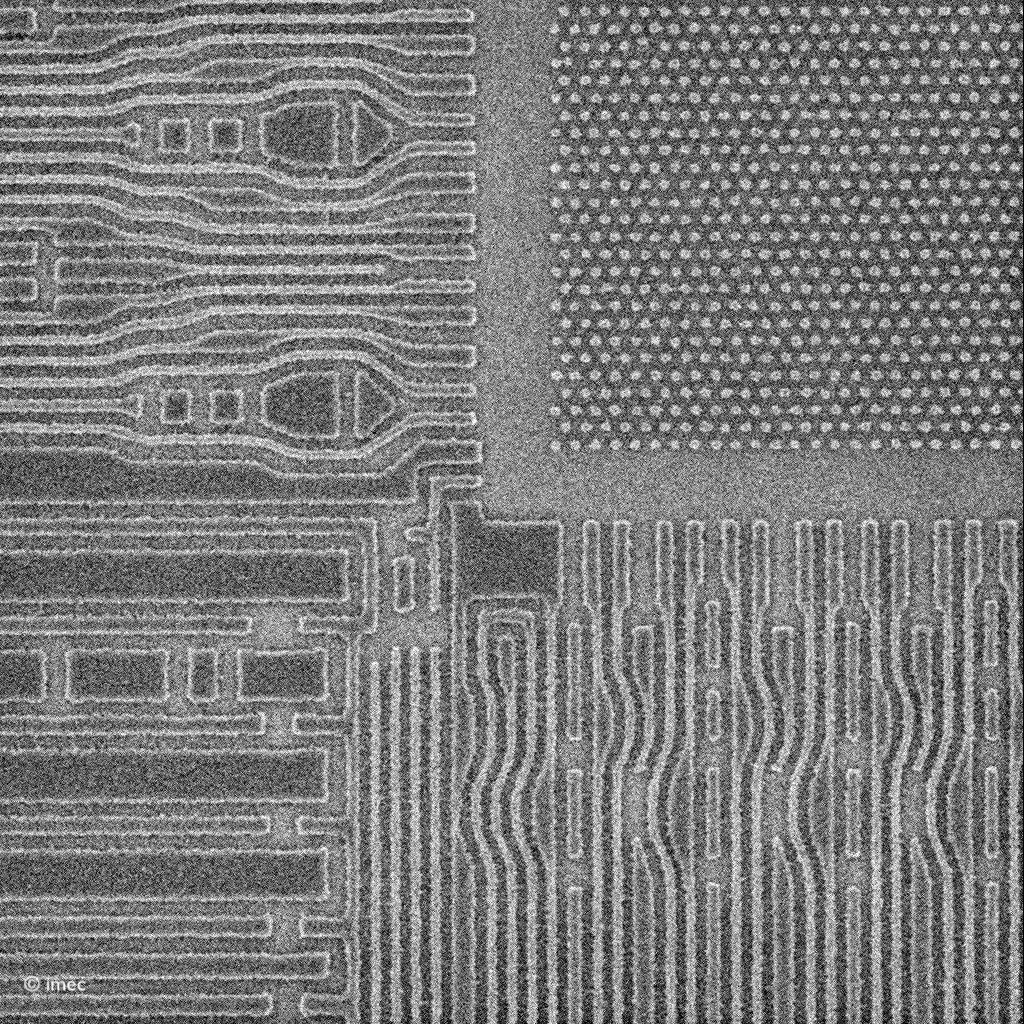

Imec heeft in een gezamenlijk lab met ASML patroonstructuren aangebracht op 9,5 nanometer (19 nanometer pitch), random vias met 30 nanometer center-to-center afstand, 3D features op een 22 nanometer pitch en een DRAM specifieke layout op P32nm en dat met een eenmalige blootstelling.

Dat is een hele complexe samenvatting om te zeggen dat imec met succes de nieuwe High NA EUV Lithography methode kan toepassen. High NA EUV lithografie is de volgende stap in het bewerken van ‘lege’ stukken silicium om er chips van te maken.

Om uit te leggen wat High NA EUV precies betekent moet je weten dat moderne geavanceerde chips worden gemaakt door er extreem ultraviolet (EUV) licht op te laten vallen. De NA staat voor numerieke apertuur. Dat is de openingshoek om het beeld scherper te maken en de belichte lijnen kleiner te maken.

De bovenvermelde cijfers in nanometer staan voor alle duidelijkheid los van de schaal die chipfabrikanten hanteren. Zo hoor je bij Qualcomm of AMD momenteel dat ze op 3 nanometer produceren, en Intel kondigde deze week aan dat het op schema zit voor 1,8 nm chips. Maar wat imec en ASML momenteel demonstreren moet in de toekomst wel degelijk naar dergelijke spelers komen. ASML heeft overigens in december ook al een High NA EUV lithografiemachine aan Intel bezorgd.

Eenmalige blootstelling

De techniek maakt het mogelijk om opnieuw meer (en veel kleinere) transistors op één chip te krijgen, wat hun prestaties verhoogt en het stroomverbruik doet dalen.

Dat dat kan door het materiaal één keer bloot te stellen (single exposure) is niet onbelangrijk. Dat beperkt het aantal stappen en dus ook het aantal mogelijke fouten in de chipproductie.

ASML, dat machines maakt om chips te produceren, en imec, dat met bijna alle chipspelers samenwerkt als neutraal onderzoeksterrein, openden begin juni hun gezamenlijk High NA EUV Lighography Lab in Veldhoven, de thuisbasis van ASML. High NA EUV moet rond 2025-2026 in massaproductie gaan, er wordt al sinds 2018 aan gewerkt.

‘Dit zal de opbrengst (de hoeveelheid werkende chips die tegelijk kunnen geproduceerd worden, nvdr.) verhogen en de cyclustijd verlagen en zelfs de CO²-uitstoot verminderen ten opzichte van bestaande multi-patterning 0.33 NA EUV methodes’, zei imec-CEO Luc Van den hove daar nog over tijdens de opening van het lab.

Imec zegt dat het naast de logische structuren, ook ontwerpen kon toebrengen die de storage node landing pad met de bit line periphery voor DRAM integreert. Dat toont volgens de chiponderzoeker aan dat de eenmalige blootstelling verschillende lagen van ‘maskers’ kan vervangen.

‘De resultaten tonen het unieke potentieel voor High NA EUV om single-print imaging van agressief geschaalde 2D features mogelijk te maken. Daarmee verbeteren we de ontwerpflexibiliteit en verminderen we de kost en complexiteit van het toebrengen van de patronen,’ zegt Steven Scheer, senior vicepresident compute technologies & systems en compute system scaling bij imec.