Op het ISC’10 supercomputing-event introduceerde Intel zijn nieuwe ‘Many Integrated Core’ (MIC) co-processorarchitectuur.

Op het ISC’10 supercomputing-event introduceerde Intel zijn nieuwe ‘Many Integrated Core’ (MIC) co-processorarchitectuur.

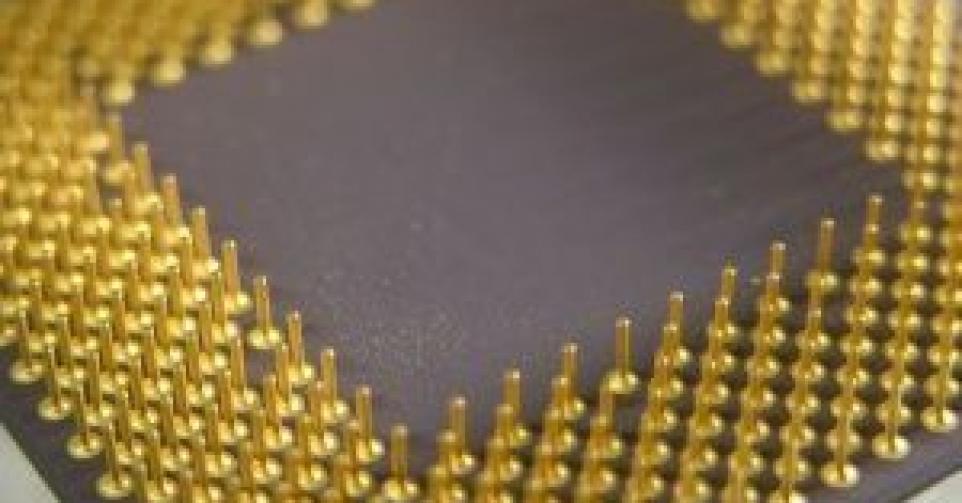

Voortboordurend op zijn multi-core chipresearch (zoals de ‘Single Chip Cloud Computer’ en de afgevoerde ‘Larrabee’ multicore grafische processor), kondigt Intel een architectuur aan die grote aantallen verwerkingskernen (voor vectoriële verwerking) combineert met een systeem van coherente caches en een snel interprocessor netwerk.

Dit geheel kan vervolgens worden aangewend met processoren voor algemene verwerkingsdoeleinden, voor het creëren van systemen met krachtige supercomputing-kenmerken.

Momenteel wordt een ontwikkelingskit geleverd (‘Knights Ferry’), met vervolgens een eerste product, ‘Knights Corner’, in 22nm technologie (met meer dan 50 verwerkingskernen per chip). Intel voorziet tevens in ontwikkelingstools, die het mogelijk moeten maken om een zelfde broncode zowel voor Xeon als voor gecombineerde Xeon/MIC systemen te optimaliseren. De nieuwe architectuur beschikt over meer dan 100 nieuwe instructies.

Op deze 25ste editie van de International Supercomputing Conference (ISC) wees Intel erop dat het bedrijf evenzeer 25 jaar geleden begon met supercomputing-activiteiten, met de toenmalige ‘Cosmic Cube’. Dat was een 80286 gesteund systeem (met 80287 numerieke co-processoren) voor een maximaal vermogen van 3,2 MegaFlops.

Vandaag maken 408 systemen uit de Top500 van supercomputers gebruik van Intel processoren en investeert het bedrijf in de ontwikkeling van elementen voor supercomputers op ‘exascale’ niveau. Zo opent Intel naast het ExaTec lab in Parijs (voor toepassingen op exaschaal) nu ook het Exacluster lab in het Duitse Jülich (voor onderzoek naar clusters met verwerkingsvermogen op Exaschaal).

Met de nieuwe Sandy Bridge architectuur in 22nm, evenals met introductie van de Advanced Vector Extensions, voorziet Intel ook een bredere basis voor de ontwikkeling van supercomputingsystemen.